Megatrends wie Konnektivität und Digitalisierung, Elektrifizierung, Automatisierung und Energieeffizienz eröffnen erhebliche Chancen und Anforderungen im Bereich der Leistungselektronik. Die Branche sieht sich zunehmend der Aufgabe gegenüber, höchste Effizienz mit kleineren Systemgrößen, verbesserter Zuverlässigkeit, längerer Lebensdauer und reduzierten Systemkosten zu kombinieren. SiC-basierte Leistungswandler machen dies im Vergleich zu herkömmlichen Systemkomponenten auf Siliziumbasis möglich.

Siliziumkarbid (SiC) weist charakteristische Eigenschaften auf, die es von Silizium unterscheiden. So ist seine Bandlücke dreimal größer, was bedeutet, dass die Energie zum Anheben eines Elektrons vom Valenzband in das Leitungsband dreimal so hoch ist. Dadurch kann SiC einer zehnmal höheren elektrischen Feldstärke standhalten. SiC-basierte Bauelemente können also höhere Spannungen verarbeiten – oder mit einer dünneren und stärker dotierten Driftschicht für dieselbe Spannungsklasse hergestellt werden. Das führt dazu, dass SiC-Bauelemente bei gleichen Nennwerten wesentlich kleiner ausfallen, weniger Leitungs- und Schaltverluste erzeugen und mit höheren Schaltgeschwindigkeiten arbeiten können. Zudem erlaubt die dreimal höhere Wärmeleitfähigkeit eine effizientere Wärmeableitung pro Flächeneinheit. Dadurch können Entwickler die Vorteile von SiC nutzen, um leistungsstärkere Stromversorgungssysteme zu schaffen.

Bei der Auswahl geeigneter SiC-MOSFETs für ihre Anwendung können Ingenieure die statischen und dynamischen Standardparameter in den Datenblättern verschiedener Hersteller gezielt prüfen. Der Detailgrad und die Auswirkungen der einzelnen Parameter im Systemdesign sind jedoch weder umfassend dokumentiert noch vollständig bekannt. In diesem Anwendungshinweis werden einige dieser Parameter behandelt, darunter die Temperaturstabilität $R_{mathrm{DSon}}$, die Toleranz der Schwellenspannung, das Gate-Charge-Verhältnis, der Einfluss der Gate-Treiberspannung sowie die Robustheit der SiC-MOSFET-Body-Diode. Die in diesem Anwendungshinweis enthaltenen Empfehlungen helfen Entwicklern dabei, die richtigen SiC-Bauelemente verschiedener Anbieter auszuwählen, diese mit den SiC-Bauelementen von Nexperia zu vergleichen und maximale Vorteile zur Optimierung ihrer Systemleistung zu nutzen.

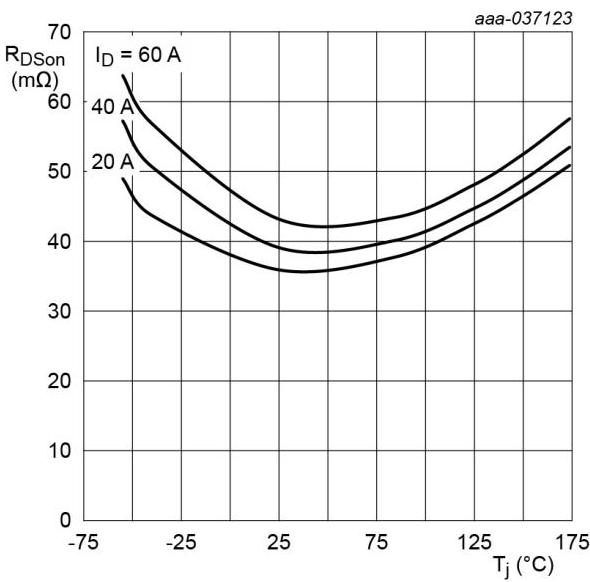

Der Einschaltwiderstand ($R_{mathrm{DSon}}$) von SiC MOSFETs ergibt sich aus den Anteilen verschiedener interner Widerstandselemente, deren Werte von der Gate-Source-Spannung ($V_{mathrm{GS}}$) abhängen. Besonders hervorzuheben sind der Kanalwiderstand ($R_{mathrm{CH}}$), der JFET-Widerstand ($R_{mathrm{J}}$) sowie der Driftzonenwiderstand ($R_{mathrm{DRIFT}}$). $R_{mathrm{CH}}$ weist einen negativen Temperaturkoeffizienten auf und dominiert $R_{mathrm{DS}}$ bei niedrigeren $V_{mathrm{GS}}$-Werten. Im Gegensatz dazu besitzen $R_{mathrm{J}}$ und $R_{mathrm{DRIFT}}$ einen positiven Temperaturkoeffizienten und sind bei höheren $V_{mathrm{GS}}$-Werten dominant. Für $V_{mathrm{GS}} > 13$ V weist der Einschaltwiderstand einen ausgeprägten positiven Temperaturkoeffizienten auf, wie in Abbildung 1 zu sehen. Dies führt zu einem negativen Rückkopplungseffekt bei der Stromverteilung zwischen parallelen Bauelementen. Während des Parallelbetriebs führt eine Erhöhung der Sperrschichttemperatur in einem MOSFET infolge des positiven Temperaturkoeffizienten zu einer Steigerung des Einschaltwiderstands $R_{mathrm{DS}}$. Dies reduziert den Stromfluss und verlagert ihn auf den parallel betriebenen MOSFET, bis sich ein stabiler Gleichgewichtszustand einstellt.

Die Temperaturabhängigkeit des Einschaltwiderstands hängt zudem von der Durchbruchspannung und der Art des Bauelements ab. Beispielsweise haben 1200-V-Bauelemente einen höheren Temperaturkoeffizienten, da der Widerstand der Driftschicht im Vergleich zu Bauelementen niedrigerer Spannungshöhe größer ist.

Zusätzlich erhöht sich bei hohen Temperaturen der $R_{mathrm{DSon}}$, um den maximalen Sättigungsstrom zu begrenzen. Dies verbessert gleichzeitig die Kurzschlussfestigkeit des Bauelements.

Abbildung 1. Der Einschaltwiderstand $R_{mathrm{DSon}}$ im Verhältnis zur Sperrschichttemperatur $T_j$, mit dem Drain-Source-Strom $I_{mathrm{DS}}$ als Parameter

Siliziumkarbid (SiC) ist bekannt für seine Temperaturstabilität. Dennoch steigt bei Bauelementen in der Leistungselektronik der Einschaltwiderstand $R_{mathrm{DSon}}$ wenn sich der Chip während des Betriebs erwärmt (typischerweise um das 1,6- bis 2-fache).

So kann ein Bauteil, das bei 25 °C einen Widerstand von 40 mΩ hat, bei einer Sperrschichttemperatur von 175 °C auf 80 mΩ ansteigen.

Nexperia 1200-V-SiC-MOSFETs zeichnen sich hier aus: Im Vergleich zu anderen Bauteilen weisen sie den geringsten $R_{mathrm{DSon}}$-Temperaturdrift auf. Ein Beispiel: Ein Nexperia-Bauteil mit 40 mΩ bei 25 °C erreicht bei einer Sperrschichttemperatur von 175 °C nur 56 mΩ. Das entspricht einem Temperaturdrift von lediglich Faktor 1,4, wie in Abbildung 2 zu sehen ist.

Diese $R_{mathrm{DSon}}$ Temperaturstabilität führt zu einem entscheidenden Vorteil: Im Vergleich zu Bauelementen anderer Hersteller haben diese SiC-Produkte bei hohen Temperaturen geringere Leitungsverluste. Dadurch eignen sich die SiC-Bauelemente von Nexperia ideal für anspruchsvolle Anwendungen in der Leistungselektronik, wie zum Beispiel bei Motorantrieben, Ladeinfrastrukturen, Solaranlagen oder unterbrechungsfreien Stromversorgungen.

Abbildung 2. Normalisierter Drain-Source-Widerstand im eingeschalteten Zustand als Funktion der Sperrschichttemperatur; typische Werte

Die Schwellenspannung eines MOSFET ist ein wichtiger Indikator für den sicheren Betrieb des Bauelements. Ein Bereich von 2 bis 4 Volt bietet in der Regel eine akzeptable Betriebsspanne. Nexperia 1200-V-SiC-MOSFETs haben eine Schwellenspannung von 2,3 V (typisch) und gewährleisten so einen sicheren Betrieb.

Neben der Schwellenspannung stellt auch die Schwellenspannungstoleranz einen wichtigen Parameter für den sicheren Betrieb des Bauelements dar, da sie die Abweichung zwischen der spezifizierten minimalen und maximalen Schwellenspannung beschreibt.

Ein wichtiger Vorteil einer geringen Schwankung beziehungsweise Toleranz der Schwellenspannung liegt darin, dass sie ein hochsymmetrisches Schaltverhalten gewährleistet – eine Voraussetzung für den parallelen Betrieb mehrerer SiC-MOSFETs. Durch diese ausgeglichene Parallelisierung wird die Belastung der Halbleiter im dynamischen Schaltbetrieb verringert, die Schaltungsleistung verbessert und die Lebensdauer der Bauelemente verlängert.

Nexperia SiC-MOSFETs zeigen selbst unter ungünstigsten Bedingungen nur minimale Schwellenspannungsabweichungen von 1,2 V und ermöglichen dadurch eine besonders gleichmäßige Parallelisierung der Bauelemente. Die Schwellenspannung nimmt mit steigender Temperatur typischerweise ab, wie in Abbildung 3 zu sehen ist. Daher sind detaillierte Toleranzanalysen im Design notwendig. Diese stellen sicher, dass Schaltmuster sicher ablaufen und unerwünschte Einschalt-Ereignisse vermieden werden.

Abbildung 3. Die Gate-Source-Schwellenspannung als Funktion der Sperrschichttemperatur; typische Werte

Die dynamischen Eigenschaften eines Bauelements bestimmen sein Schaltverhalten. Zahlreiche dieser Parameter werden stark von den jeweiligen Messbedingungen beeinflusst. Deshalb ist ein genaues Verständnis der dynamischen Eigenschaften unerlässlich, bevor Datenblätter unterschiedlicher Hersteller miteinander verglichen werden.

Tabelle 1 zeigt eine Übersicht der typischen dynamischen Eigenschaften des Nexperia-Bauelements NSF080120L3A0.

| Symbol | Parameter | Bedingungen | Min. | Typ | Max. | Einheit |

|---|---|---|---|---|---|---|

| Dynamische Eigenschaften | ||||||

| $Q_{mathrm{G(tot)}}$ | Gesamt-Gate-Ladung | $V_{mathrm{DD}}$ = 800 V; $I_{mathrm{D}}$ = 20 A; $V_{mathrm{GS}}$ = -5/+15 V; $T_j$ = 25 °C | – | 52 | – | nC |

| $Q_{mathrm{GS}}$ | Gate-Source-Ladung | – | 22 | – | nC | |

| $Q_{mathrm{GD}}$ | Gate-Drain-Ladung | – | 16 | – | nC | |

| $C_{mathrm{iss}}$ | Eingangskapazität | $V_{mathrm{DD}}$ = 800 V; f = 0,5 MHz; $V_{mathrm{GS}}$ = 0 V; $T_j$ = 25 °C | – | 1335 | – | pF |

| $C_{mathrm{oss}}$ | Ausgangskapazität | – | 74 | – | pF | |

| $C_{mathrm{rss}}$ | Rückübertragungskapazität | – | 4 | – | pF | |

| $t_{mathrm{d(on)}}$ | Einschaltverzögerungszeit | $V_{mathrm{DD}}$ = 800 V; $I_{mathrm{D}}$ = 20 A; $R_{mathrm{G(ext)}}$ = 2,2 Ω; $V_{mathrm{GS}}$ = -5/+15 V; L = 82 µH; $T_j$ = 25 °C | – | 30 | – | ns |

| $t_{mathrm{r}}$ | Anstiegszeit | – | 14 | – | ns | |

| $t_{mathrm{d(off)}}$ | Ausschaltverzögerungszeit | – | 15 | – | ns | |

| $t_{mathrm{f}}$ | Abfallzeit | – | 14 | – | ns | |

| $E_{mathrm{on}}$ | Einschaltverluste | – | 445 | – | µJ | |

| $E_{mathrm{off}}$ | Ausschaltverluste | – | 38 | – | µJ |

Tabelle 1. Dynamische Eigenschaften

Ein wichtiger Aspekt bei der Einführung von schnellem Schalten in einer Anwendung ist der Einfluss der Schalttransienten auf die parasitären Elemente des Systems sowie auf die Body-Kapazitäten der Bauelemente. Die Auswirkungen dieser Body-Kapazitäten auf die Systemdynamik lassen sich zur besseren Verständlichkeit in den folgenden Punkten zusammenfassen und sind zusätzlich in Tabelle 2 zu sehen.

Die Gate-Source-Kapazität – $C_{mathrm{gs}}$ ($C_{mathrm{iss}}$ – $C_{mathrm{rss}}$) bestimmt die Verzögerungszeit sowie den di/dt-Wert. Wird ein Bauelement mit einer größeren $C_{mathrm{gs}}$ gewählt, verringert sich die Schaltgeschwindigkeit. Die Gate-Source-Kapazität $C_{mathrm{gs}}$ hat keinen wesentlichen Einfluss auf die Spannungsanstiegsgeschwindigkeit. Die Gate-Drain-Kapazität $C_{mathrm{gd}}$ ($C_{mathrm{rss}}$) auch bekannt als „Miller-Kapazität“, bestimmt den Wert von dv/dt. $C_{mathrm{gd}}$ ist deutlich kleiner als $C_{mathrm{gs}}$ und $C_{mathrm{ds}}$.

Daher führt bereits eine geringe Änderung des $C_{mathrm{gd}}$-Wertes zu einem großen Effekt auf den dv/dt-Wert. $C_{mathrm{gd}}$ hat keine offensichtliche Beziehung zur Verzögerungszeit oder zu di/dt.

Die Drain-Source-Kapazität – $C_{mathrm{ds}}$ ($C_{mathrm{oss}}$ – $C_{mathrm{rss}}$) beeinflusst ebenfalls den dv/dt-Wert, steht aber in keiner klaren Beziehung zur Verzögerungszeit oder zu di/dt. Eine zusätzliche $C_{mathrm{ds}}$ wird bisweilen eingesetzt, um durch deren Erhöhung ein weiches Ausschalten zu erreichen. Durch die Erhöhung von $C_{mathrm{ds}}$ verringert sich die dv/dt-Rate sowohl beim Ein- als auch beim Ausschalten. Dadurch werden die Ausschaltverluste als auch der Spannungsüberschwingen beim Ausschalten reduziert. Allerdings führt die während der Ausschaltphase in $C_{mathrm{ds}}$ gespeicherte Ladung beim Einschalten zu einem deutlichen Stromüberschwinger, was wiederum eine spürbare Erhöhung der Einschaltverluste bedeutet.

| $(di/dt)_{mathrm{on}}$ | $(dv/dt)_{mathrm{on}}$ | $(di/dt)_{mathrm{off}}$ | $(dv/dt)_{mathrm{off}}$ | $E_{mathrm{on}}$ | $E_{mathrm{off}}$ | |

|---|---|---|---|---|---|---|

| $C_{mathrm{gs}}$ ↑ | ↓ | — | ↓ | — | ↑ | ↑ |

| $C_{mathrm{gd}}$ ↑ | — | ↓ | — | ↓ | ↑ | ↑ |

| $C_{mathrm{ds}}$ ↑ | — | ↓ | — | ↓ | ↑ | ↑ |

Tabelle 2. Einfluss der der Schaltungsparameter auf das Schaltverhalten

Die Eingangskapazität allein reicht nicht aus, um die Schaltleistung von Bauelementen verschiedener Hersteller genau zu vergleichen. Effekte wie die Größe der Bauelemente und die Transkonduktanz können das Ergebnis verfälschen. Aus der Sicht des Schaltungsdesigns ist die Gate-Ladung daher ein deutlich nützlicherer Parameter als die Kapazität. Die meisten Hersteller geben beide Werte in ihren Datenblättern an. Der Vorteil der Gate-Ladung liegt darin, dass Entwickler einfach den Strombedarf des Gate-Treiber-Schaltkreises berechnen können, um das Bauelement innerhalb einer gewünschten Zeit einzuschalten.

$Q_{mathrm{G(tot)}}$, $Q_{mathrm{GS}}$ und $Q_{mathrm{GD}}$ stammen alle aus derselben Gate-Ladekurve, die typischerweise im Datenblatt zu finden ist. Sie beschreiben, wie viel Gate-Ladung der MOSFET unter bestimmten Bedingungen zum Schalten benötigt. Die Gate-Ladungsparameter hängen sowohl von der Schwellenspannung, den Ansteuerspannungen und der Schaltcharakteristik als auch von der zu schaltenden Last ab. Da sich die Kapazitäten mit Spannung und Strom verändern, ist es zur Beurteilung der Schaltleistung sinnvoller, die Gate-Ladungsdaten anstelle der Kapazitätsdaten heranzuziehen. Dies gilt insbesondere dann, wenn der Gate-Treiber des MOSFETs in seinem Strom begrenzt ist und ein schnelles Schalten erforderlich ist. Die Gesamt-Gate-Ladung $Q_{mathrm{G}}$ setzt sich aus den Werten $Q_{mathrm{GS}}$ und $Q_{mathrm{GD}}$ zusammen. Dabei repräsentiert $Q_{mathrm{GS}}$ die Ladungsansammlung in der Gate-Source-Kapazität, während $Q_{mathrm{GD}}$ die Ladungsansammlung in der Gate-Drain-Kapazität darstellt. Für den Einsatz bei hohen Frequenzen sollte die Gesamt-Gate-Ladung $Q_{mathrm{G}}$ so klein wie möglich sein. Eine niedrige Gate-Ladung oder $Q_{mathrm{G}}$ reduziert die Verluste des Gate-Treibers während des Schaltvorgangs. Dies senkt den Stromverbrauch und die Anforderungen an den Gate-Treiber.

Eine weitere, oft übersehene Kennzahl für die Schaltleistung ist das Verhältnis zwischen der Gate-Drain-Ladung ($Q_{mathrm{GD}}$) und der Gate-Source-Ladung ($Q_{mathrm{GS}}$). Bauelemente erreichen die höchste Stabilität ohne unerwünschte Miller-Einschaltinstabilitäten, wenn die Gate-Drain-Ladung kleiner oder nahezu identisch mit der Gate-Source-Ladung ist.

Dank ihrer relativ geringen Gate-Ladung und dem ausgewogenen Verhältnis von $Q_{mathrm{GD}}$ zu $Q_{mathrm{GS}}$, liegen die 1200-V-SiC-MOSFETs von Nexperia innerhalb des optimalen Ladebereichs für Siliziumkarbid-Bauelemente. Das bedeutet: Im Vergleich zu anderen Siliziumkarbid-Bauteilen auf dem Markt bieten die Bauelemente von Nexperia die beste Kombination aus niedrigem Stromverbrauch, hoher Robustheit und sicherer Schaltleistung. Bei der Auswahl eines Bauelements für Hard-Switching-Anwendungen liefern $Q_{mathrm{GD}}$ und $R_{mathrm{DSon}}$ einen besseren Hinweis auf die Gütezahl (Figure of Merit) des Bauelements. Für Soft-Switching-Wandler liefern $Q_{mathrm{oss}}$ zusammen mit $Q_{mathrm{GD}}$ und $R_{mathrm{DSon}}$ einen besseren Indikator für die Eignung des Bauelements.

In diesem Abschnitt wird der Einfluss der Gate-Treiber-Spannung auf die statischen und dynamischen Verluste von SiC-MOSFETs erläutert. Einerseits ist eine hohe Gate-Source-Spannung $V_{mathrm{GS}}$ im ON-Zustand erforderlich, um eine vollständige Kanalinversion, geringe Einschaltverluste und schnelles Schalten zu gewährleisten. Andererseits reduziert eine niedrigere Gate-Source-Spannung $V_{mathrm{GS}}$ im ON-Zustand die elektrische Belastung des Gate-Oxids und erhöht die Langzeitstabilität.

Bei der Auswahl der optimalen Gate-Treiber-Spannung für die beste Leistung sollte das Temperaturverhalten des $R_{mathrm{DSon}}$ berücksichtigt werden, wie in Abbildung 4 dargestellt. Unterhalb einer Gate-Spannung von 13 V steigt der Drain-Strom mit der Temperatur.

Es wird nicht empfohlen, $V_{mathrm{GS}}$ im eingeschalteten Zustand unter +13 V zu betreiben. Generell kann das Bauelement mit Gate-Source-Spannungen über 15 V angesteuert werden, was das Einschaltverhalten weiter verbessert (siehe Abbildung 5).

Abbildung 4. Drain-Source-Einschaltwiderstand in Abhängigkeit von der Gate-Source-Spannung

Abbildung 5. Drain-Source-Einschaltwiderstand in Abhängigkeit vom Drain-Strom; typische Werte

Abbildung 6 und Abbildung 7 veranschaulichen, wie sich eine Änderung der Gate-Treiber-Spannung auf die Schaltverluste ($E_{mathrm{off}}$ und $E_{mathrm{on}}$) des Nexperia-Bauelements TO-247, 3-Pin, 40 mΩ auswirkt. Für dieses Gehäuse gilt: Bleibt der externe Gate-Widerstand $R_{mathrm{G(ext)}}$ konstant bei 2,2 Ω, sinken die Einschaltverluste ($E_{mathrm{on}}$), wenn die Ansteuerspannung $V_{mathrm{G(on)}}$ erhöht wird. Bei 18 V ist $E_{mathrm{on}}$ im Vergleich zu 15 V um den Faktor 1,4 reduziert. Im Gegensatz dazu zeigen die Ausschaltverluste $E_{mathrm{off}}$ nur geringe Abweichungen in Abhängigkeit von $V_{mathrm{G(on)}}$.

Abbildung 6. Ausschaltenergie in Abhängigkeit vom Drain-Strom; typische Werte

Abbildung 7. Einschaltenergie in Abhängigkeit vom Drain-Strom; typische Werte

Das Verständnis des Einflusses der gewählten Gate-Spannung auf das Leistungsbauelement ist entscheidend, um ein optimales Gleichgewicht zwischen elektrischer Leistung und Zuverlässigkeit zu erreichen. Beschleunigte Stresstests eignen sich, um den Einfluss von $V_{mathrm{GS}}$-Belastungen auf die Schwellenspannung sowie die Zuverlässigkeit des Gate-Oxids zu untersuchen, insbesondere bei hohen Temperaturen.

SiC-MOSFETs kommen häufig in symmetrischen Brückenschaltungen zum Einsatz, bei denen ein High-Side- und ein Low-Side-Bauelement komplementär schalten. Eine Totzeit, in der beide Bauelemente abgeschaltet sind, ist erforderlich, um Kurzschlüsse zu vermeiden. Während dieser Totzeit fließt der Strom weiterhin durch die Body-Diode der MOSFETs. Der Spannungsabfall des Bauelements ist in diesem Zustand höher, als wenn der Kanal eingeschaltet wäre. Dieser erhöhte Spannungsabfall während der Totzeit führt zu höheren Verlusten.

Abbildung 8. Source-Strom in Abhängigkeit von der Source-Drain-Spannung; typische Werte (Kennlinie im dritten Quadranten)

Abbildung 9. Source-Strom in Abhängigkeit von der Source-Drain-Spannung; typische Werte (Kennlinie im dritten Quadranten)

Dank ihrer herausragenden Robustheit weisen die Body-Dioden der Nexperia 1200 V SiC-MOSFETs einen geringeren Spannungsabfall auf als vergleichbare SiC-Bauelemente anderer Anbieter.

Bei einem Betrieb mit 25 A und 85 °C beträgt der Spannungsabfall der Nexperia SiC-MOSFETs nur etwa 3,5 V, während andere Hersteller mit gleichem $R_{mathrm{DSon}}$ leicht über 5 V erreichen. Daher sind die Verluste während der Totzeitphase der Nexperia 1200 V SiC-MOSFETs im Vergleich zu anderen unter denselben Bedingungen und mit derselben Totzeit eingesetzten Bauelementen deutlich geringer. Diese geringeren Verluste verhindern die Entstehung von übermäßiger Wärme und bieten den Entwicklern mehr Flexibilität bei der Wahl der benötigten Totzeit.

Die Sperrverzögerungsladung der Body-Diode ($Q_{mathrm{rr}}$) ist ein wichtiger Parameter für Brückentopologien mit harter Kommutation. Dank der geringen $Q_{mathrm{rr}}$ der SiC MOSFETs sinken die Schaltverluste, was eine Erhöhung der Schaltfrequenz ermöglicht. Je höher die Temperatur, desto größer ist die Reverse-Recovery-Ladung. Glücklicherweise sind die absoluten Werte bei Nennstrom immer noch relativ niedrig, sodass die Nexperia-MOSFETs deutlich geringere, nahezu vernachlässigbare Reverse-Recovery-Verluste aufweisen. Gleichzeitig ist zu erwarten, dass das Risiko von Ausfällen und durch den Recovery-Strom verursachten Störungen reduziert wird.

Dieser Anwendungshinweis zeigt die Auswirkungen zentraler SiC-MOSFET-Parameter und erklärt, wie Entwickler damit Bauelemente verschiedener Hersteller vergleichen können. Vorausgesetzt, die gängigen Designrichtlinien und bewährten Layout-Praktiken wurden eingehalten, ermöglichen die Informationen dieses Anwendungshinweises, die maximale Leistung aus dem SiC-MOSFET in jeder Leistungsumwandlungsanwendung zu erzielen.